点击上方“轩哥谈芯”,关注后了解更多精彩内容,!!

在设计CAN这个东西的时候,很多人一上来就会问一句:“现在 MCU 都有内部时钟了,为啥还要外挂晶振?”

表面看是个器件选型问题,本质其实是通信物理层 + 时序预算 + 工程容错三件事叠在一起的结果。

你要是只从“能不能跑起来”去看,内部 RC 也许能勉强工作一会儿;但你要从“量产、稳定、不丢帧”去看,这件事基本就没得选了。

先把核心矛盾说清楚:CAN 是一个“各玩各的时钟,但必须对齐采样”的系统,这一点跟我们的串口一样。

每个节点都拿自己的时钟去采样总线,但总线只有一条。

换句话说——你以为你在第 N 个 bit 采样,别人也必须在同一个时间点认为这是第 N 个 bit。

这里面没有“统一时钟源”,它不像 IIC和 SPI,有个单独的 CLK 信号来通知双方,来活啦!它靠的全是:

位填充(bit stuffing)

边沿同步(resync)

相位补偿(SJW)

这些机制本质上是在“纠错”,不是在“兜底”。

它们能修小误差,但修不了大偏差。

时钟源这个问题在 CAN FD 这里被放大了,经典 CAN,1Mbps,一位时间是 1000ns。

而CAN FD,数据段直接拉到 5Mbps,一位只剩 200ns。

这意味着什么?

你可以这么理解:

以前你有 1000ns 时间窗口去“猜这个 bit”

现在只给你 200ns

时间窗口缩短了 5 倍,但误差并不会自动缩小 5 倍。

结果就是——

原来还能靠同步机制“抹平”的误差,现在直接顶到边界,来不及修正。

很多人觉得“误差不就是一点点频偏吗”,但这里有个工程上经常被忽略的点:误差是“累积”的。

不是你某一个 bit 偏了一点,而是:

每个 bit 都在偏

偏差在整个帧里不断积累

到后面直接采样错位

CAN 的重同步是基于边沿触发的,但数据段一旦进入连续位(特别是 FD 数据段),

边沿变少 → 同步机会减少 → 误差更容易跑飞。

这才是 CAN FD 真正苛刻的地方。

再往下就是一个很现实的数字问题了。

CAN FD 在工程上通常要求时钟精度做到:

±0.1%(1000 ppm)以内

实际很多设计会压到 ±0.05%(500 ppm)

而你再看看几种时钟源的量级:

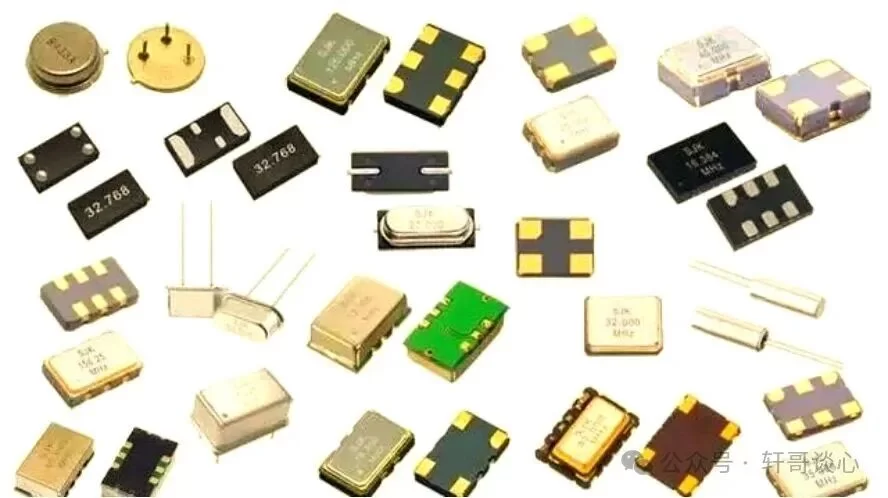

内部 RC:±1% ~ ±5%(1万 ~ 5万 ppm)

陶瓷谐振器:±0.1% ~ ±0.5%(1000 ~ 5000 ppm)

石英晶振:±10 ~ 50 ppm

这里不是“差一点”,是差一个数量级甚至两个数量级。

也就是说:

👉 内部 RC 的误差,还没开始通信,就已经把 CAN FD 的容差吃光了

👉 陶瓷振荡器基本属于“运气好能跑,温漂一来就翻车”

👉 只有石英晶振,是在误差预算里“有余量”的

工程上真正让人崩溃的,其实不是“跑不起来”,而是这种场景:

实验室 OK

常温 OK

换个板子、换个批次、温度一变 → 开始掉帧、Bus Off

这种问题你根本不好定位,因为它不是逻辑 bug,是时序边界被吃掉了。

而内部 RC 最大的问题,不只是初始精度差,而是:

温漂大

电压敏感

批次离散性大

也就是说,它的误差不是常数,是在随机“飘”的。

CAN FD 这种协议,本质是个强约束系统,最怕的就是这种不确定性。

所以你会看到一个很典型的工程结论:

CAN FD 用外部晶振,不是为了“更好”,而是为了“刚好能用”。

石英晶振的价值在这里其实就一句话:

👉 把你的系统,从“踩线运行”,拉回到“有裕量运行”

这点在你做下面这些功能时,会特别明显:

高速数据段(>2Mbps)

硬件时间戳(时间一致性要求高)

多节点大网络(误差叠加更严重)

最后给一个普通人的理解方式。

你可以把 CAN FD 想成一个多人同时拍手的系统:

每个人按自己的节奏拍(本地时钟)

但必须“听起来是整齐的”(同步采样)

内部 RC 就像每个人带个不准的机械表,而且还会随温度变快变慢;

石英晶振相当于大家都带校过的电子表。

低速的时候,大家还能靠“听声音”勉强对齐;

一旦啪啪啪的加快,没有准表,这个系统一定散架。

© 版权声明

文章版权归作者所有,未经允许请勿转载。

相关文章

没有相关内容!